Physical Verification (PV) is a fundamental method in the Chip Design cycle both in Analog, and Digital arrangement streams, wherein IC Layout or Routed Design is checked for collecting rules criteria as controlled by the foundry.

Physical Verification joins Design Rule Checks (DRC), Layout Versus Schematic (LVS), Electrical Rule Checks (ERC), Antenna Checks, DFM, ESD, Latch-up and diverse coordination streams at SOC level. EDA gadgets are used to check these astounding gauges and fix the encroachment utilizing the configuration article chief gadgets. Physical design engineer in Bangalore is a fundamental bit of the closedown checks for IC structure before tapeout, to be made in the shop.

Normally PV checks are done by Physical Design (PD) works in cutting edge plans and by Layout works in Analog structures. In any case, some various associations have submitted PV structures as a critical part of their work approaches.

In latest advancement centre points, particularly 7nm and underneath with FINFET development being used, PV has ended up being progressively required with logically the number of precepts to check, and this has opened up a tolerable proportion of openings for work for PV works in the VLSI business.

QSOCS is the principal association to offer the physical confirmation instructional class in Bangalore. We arranged our physical check instructional class as indicated by the latest business essentials and passed on by a senior master, who has critical inclusion in Physical Verification. It gives a full prologue to an authority over organization thoughts and streams, recognized by the business.

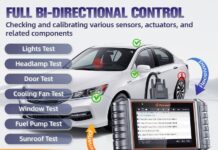

Features and Benefits

- Supports the open standard TCL/TK extensive scale language for full contraption customization.

- Gets to data inside the GDSII or OASIS® database

- Radically diminishes time to tape-out with dynamic revision and cycle circle capacities.

- Grants beneficial re-affirmation of the full arrangement, or simply the data that has been adjusted

- Beneficially automates chip finishing assignments

Why QSOCS for Physical system Verilog course?

QSOCS 100% helper, is one of the developed VLSI getting ready associations in India started by technocrats of VLSI industry experience. With best physical verification training in

Bangalore, QSoCS offers total industry-masterminded planning programs in Physical Design, Design Verification, and Custom Layout. With the alterations in the semiconductor business scene, the capacity essentials of the business have moreover changed unquestionably. The informational establishments in India with the static methods for teaching are not prepared to give decidedly ready HR as per the business necessities. Reviving the scope of capacities of the understudies as indicated by the business necessities has ended up being necessary.

QSOCS is setting up the best physical confirmation preparing the organization to beat any issues between the business necessities and the understudy scope of capacities. Our industry-focused planning programs are organized and made by the business technocrats to focus on the general progression of the hopefuls by updating their social and specific aptitudes, making them work arranged. Our courses lay emphasis on the urgent learning of VLSI and how it will, in general, be used to execute the best structure practices.

In the brief time frame, QSOCS transformed into the main association giving occupation organized VLSI getting ready to understudies making them industry-arranged creators.

Come and join up with the best physical verification training!